氮化鎵芯片制造全過程 技術開發的核心與未來展望

氮化鎵(GaN)作為一種第三代寬禁帶半導體材料,憑借其高擊穿電場、高電子飽和漂移速度以及優異的耐高溫和抗輻射性能,正成為功率電子、射頻通信和光電子等領域技術革新的關鍵驅動力。其芯片制造全過程,融合了材料科學、微納加工與器件物理的前沿技術,構成了一個精密而復雜的系統工程。

一、 技術開發的基石:材料制備與外延生長

氮化鎵芯片制造始于高質量單晶材料的制備。由于缺乏同質襯底,業界普遍采用異質外延技術,主要路徑包括:

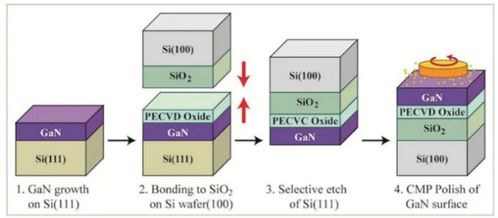

- 襯底選擇:藍寶石(Al?O?)、碳化硅(SiC)和硅(Si)是主流襯底。硅襯底因其大尺寸、低成本以及與現有硅基產線兼容的潛力,成為大規模商業化的重要方向,但晶格失配和熱膨脹系數差異是技術挑戰。

- 外延生長:金屬有機化學氣相沉積(MOCVD)是生產高質量氮化鎵外延層的核心技術。通過精確控制反應室溫度、壓力、氣體流量與比例,在襯底上逐層生長出氮化鎵緩沖層、溝道層、勢壘層等復雜異質結構,形成如高電子遷移率晶體管(HEMT)的核心功能層。

二、 核心制造工藝:微納加工與器件成型

獲得高質量外延片后,進入芯片的微觀結構構建階段,關鍵技術環節包括:

- 隔離工藝:通過離子注入或臺面蝕刻(Mesa Isolation)形成器件之間的電學隔離區域,防止串擾。

- 歐姆接觸形成:源極和漏極需要形成低電阻的歐姆接觸。通常采用鈦(Ti)/鋁(Al)/鎳(Ni)/金(Au)等多層金屬堆棧,經過快速熱退火(RTA)使金屬與氮化鎵材料合金化,降低接觸電阻。

- 柵極制造:作為控制電流的開關,柵極工藝至關重要。常采用肖特基接觸,使用鎳(Ni)/金(Au)或鉑(Pt)等金屬。為提高器件頻率和功率性能,T型柵、場板等復雜柵結構被廣泛應用,這需要高精度的電子束光刻或步進式光刻技術。

- 表面鈍化與介質沉積:氮化鎵表面態會影響器件性能和可靠性。通過等離子體增強化學氣相沉積(PECVD)等方法沉積氮化硅(SiN?)等鈍化層,以穩定表面、抑制電流崩塌。層間介質(ILD)的沉積為多層互連打下基礎。

- 互連與鈍化:通過光刻、刻蝕和金屬化(如鋁或銅)工藝形成源、柵、漏的電極壓焊盤(Pad)以及器件間的互連線,最后覆蓋鈍化層(如聚酰亞胺)進行保護。

三、 后端工藝與測試封裝

制造完成的晶圓需要經過:

- 測試:進行晶圓級電學參數測試(如飽和電流、擊穿電壓、閾值電壓等),標記不良芯片。

- 減薄與劃片:將晶圓背面減薄以利于散熱和封裝,然后用激光或金剛石刀片將晶圓切割成單個芯片(Die)。

- 封裝:根據應用需求(如射頻功率放大器、快速充電器),采用不同的封裝形式,如陶瓷封裝、塑料封裝或晶圓級封裝(WLP),實現芯片與外部世界的電學連接、機械保護和高效散熱。

四、 技術開發的關鍵挑戰與未來趨勢

當前氮化鎵芯片技術開發聚焦于:

- 提升材料質量與降低缺陷密度:研發更優的襯底(如自支撐GaN襯底)和緩沖層技術,以提升器件性能和可靠性。

- 增強工藝集成與成本控制:推動8英寸硅基氮化鎵晶圓制造技術成熟,實現與CMOS產線的深度融合,降低成本。

- 開發新器件結構與集成技術:探索垂直結構GaN器件(如CAVET)以提升功率密度,以及GaN-on-Si與硅基邏輯電路的異質集成,實現單片系統(SoC)。

- 攻克可靠性瓶頸:深入研究動態電阻退化、柵極漏電等失效機制,通過材料、工藝和電路設計的協同優化提升長期可靠性。

###

氮化鎵芯片制造全過程,從外延生長到最終封裝,每一個環節都凝聚著材料、工藝與設計的深度創新。隨著技術開發的持續突破,氮化鎵正從特定領域的“高性能選項”走向更廣泛的規模化應用,有望在5G/6G通信、新能源汽車、數據中心能源管理及消費電子快充等領域,開啟高效節能的半導體新時代。其制造技術的演進,不僅是單一材料的勝利,更是半導體產業向更高性能、更高效率邁進的一個縮影。

如若轉載,請注明出處:http://www.vzmkjt.cn/product/56.html

更新時間:2026-01-07 01:42:12